현존하는 CPU 중에 CISC는 없다.

컴퓨터 공학에서 CPU를 배우는 과정에 CISC와 RISC가 있다.

대체적으로 ARM은 RISC고 x86은 CISC라구 배운다.

난 대다수 x86을 CISC라구 말한다면 난 글쎼라는 말로 대답한다.

그 이유는 놀랍게두 x86은 CISC를 decording해서 RISC로 바꾸어주는 칩이 존재하기 때문이다.

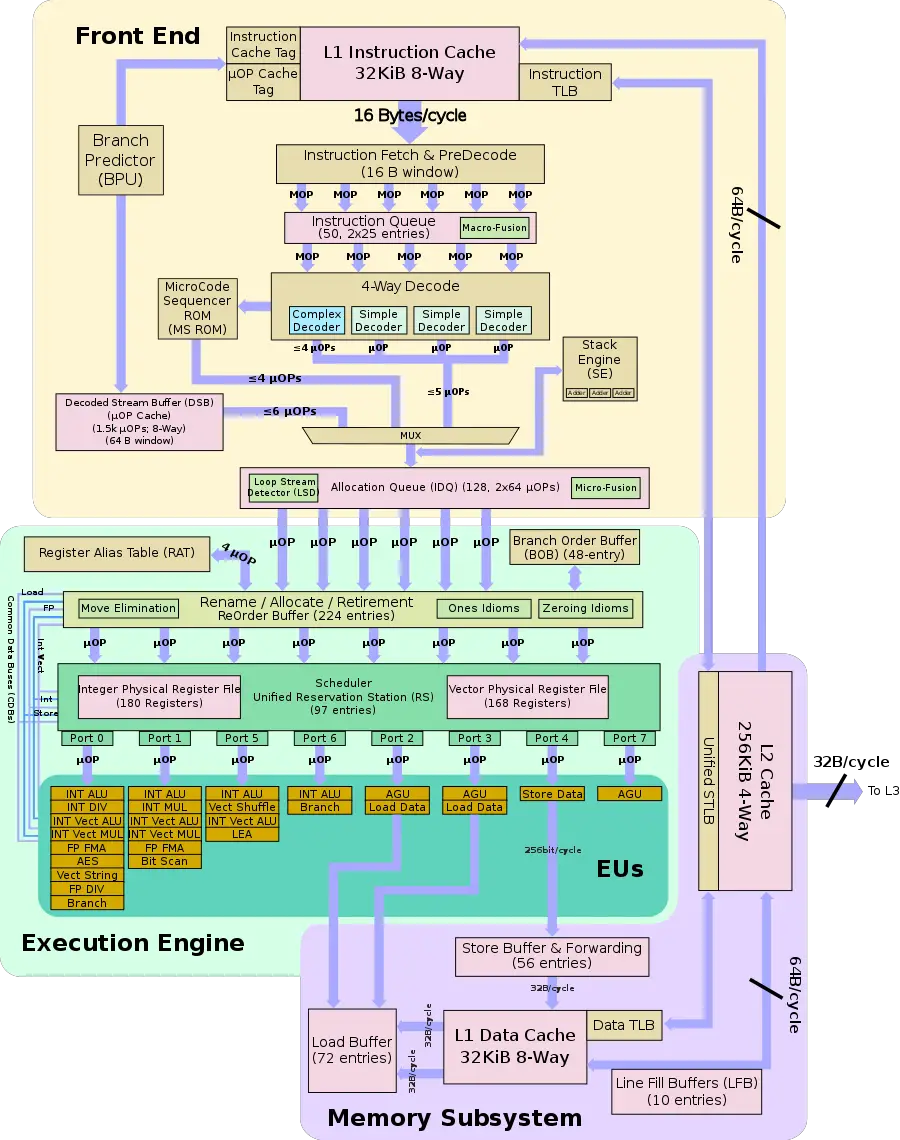

아래는 인텔 Skylake 아키텍처이다.

CPU레벨에 Front End를 보시면 4-way decode이 존재한다. 여기서 CISC를 RISC로 바꾸어준다.

이거에 대한 성능소모는 ~5%라고 추정한다(https://news.ycombinator.com/item?id=26782213)

순수히 CISC로 개발하면 파이프라이닝에 명령어의 조합으로 인해 예외처리가 발생하고 CPU내에 파이프라인을 여러개를 동시에 실행할수 있는 슈퍼 스칼라 기술에 대해 제한이 생겨버린다.

그래서 현존하는 x86은 괴랄한 방식으로 발전하게 되었는데 CPU 프론트는 x86처럼 하되 내부에서는 RSIC형태로 처리한다.

The legend of “x86 CPUs decode instructions into RISC form internally” - Fanael’s random ruminations

A dive into what x86 instruction are decoded into various processors, to determine the truth of the idea that they’re just RISC-like internally.

https://en.wikichip.org/wiki/intel/microarchitectures/skylake_(client)#Fetch_.26_pre-decoding